Display IP

퀄리타스반도체는 디스플레이 칩셋 (Display Chipset)을 위한 다양한 HSI IP를 제공합니다. 디스플레이 패널 제품이 다변화됨에 따라 응용분야가 다양해지고 있어, Display Chipset 역시 새로운 성장동력을 얻고 있습니다. 4K UHD에 이어 8K UHD 해상도를 지원하는 디스플레이 기기들의 출시로 더 선명한 화질과 해상도로 정보를 전달하려 합니다. 대표적인 디스플레이 칩셋은 크게 DTV SoC, TCON IC, DDI가 있으며 더 높은 해상도와 고화질 데이터를 전송하기 위한 초고속 인터페이스 IP와 디스플레이 칩셋 개발은 퀄리타스반도체의 중요한 과제 중 하나입니다.

퀄리타스반도체는 TCON 인터페이스의 대표적인 표준인 eDP 그리고 TCON IC에서 패널을 구동하는 DDI로 영상 신호를 전송하기 위한 Intra-Panel 인터페이스를 제공하고 있습니다.

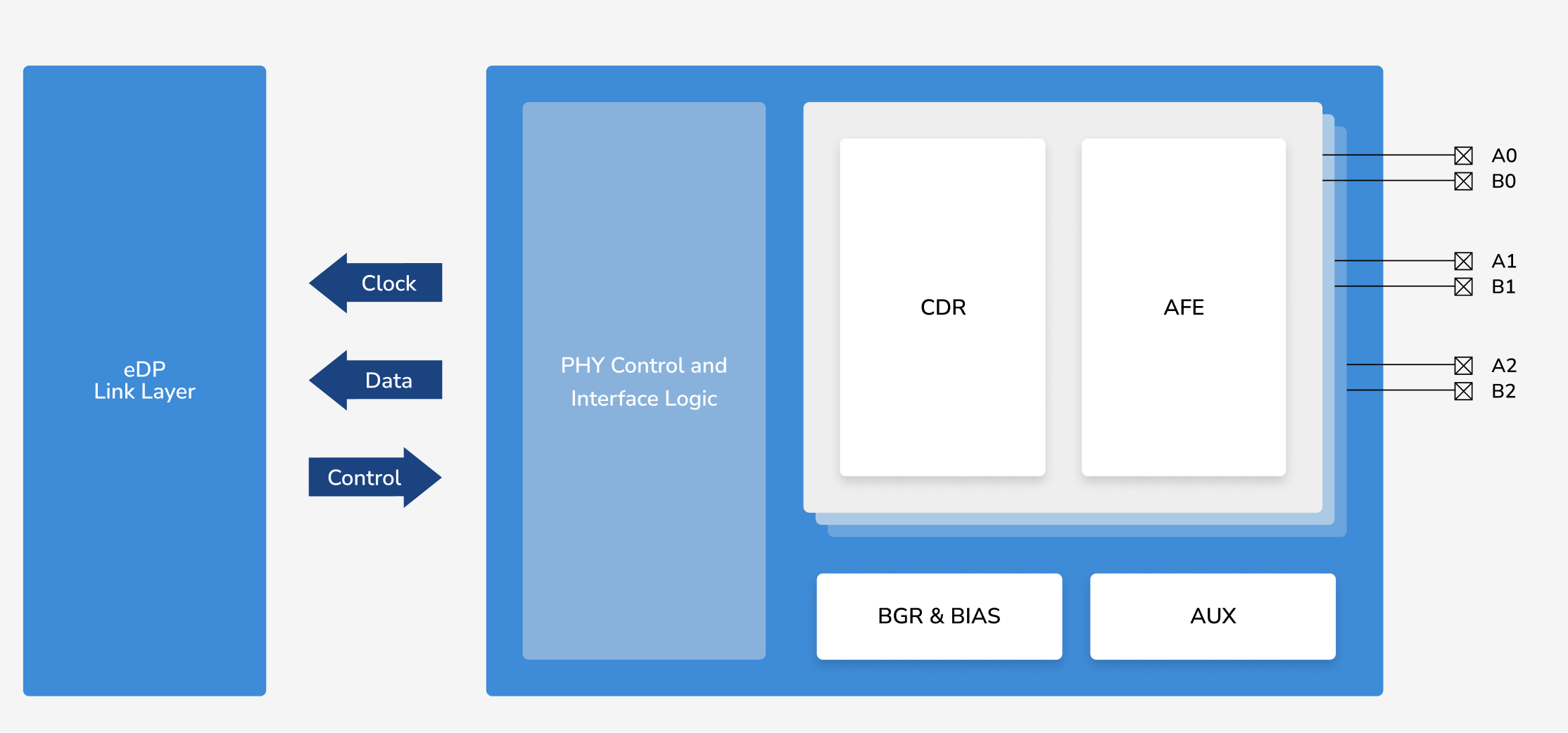

eDP RX PHY

Request DatasheetThe eDP RX PHY IP is a cost- effective and low-power solution that includes IO pads and ESD structures. With extensive built-in self-test features, including loopback and scan support, it ensures robust functionality and easy verification. This hardmacro supports the eDP RX v1.4b and v1.5a standard and is commonly used for connecting a timing controller (TCON) to a host processor.

Features

- Compliant with DisplayPort v1.4, eDP v1.4b, and eDP v1.5a

- Supports for 1.62Gbps to Max 8.1Gbps data rate

- Supports for eDP v1.4b feature such as PSR1 and PSR2

- Supports for eDP v1.5a feature such as AUX-less Link Training

- Adaptive continuous time linear equalizer (CTLE) and decision feedback equalization (DFE)

- Automatic calibration of analog circuits and offset correction

- Built-in eye open monitor

- Built-in self-test (BIST) including pseudo random bit stream (PRBS) generation and checker

Tech Specs

| Foundry Node | 14nm | |

|---|---|---|

| Standard | eDP v1.4b | eDP v1.5a |

| Max. datarate | Disclosure After NDA | |

| Status | ||

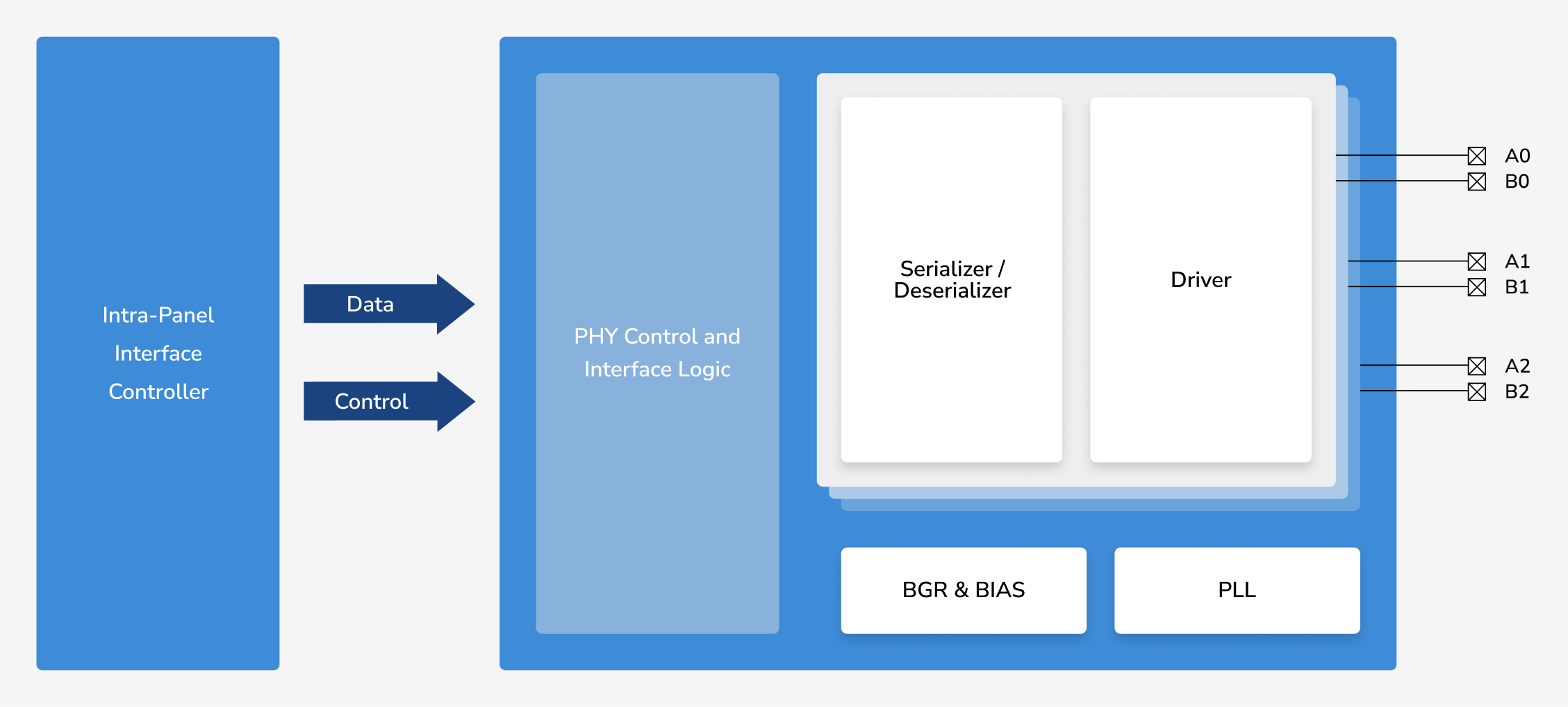

Intra-Panel TX PHY

Request DatasheetQualitas' Intra-panel TX PHY IP is an advanced chip-on-glass(ACOG) and chip-on-film(COF) transmitter embedded into the timing controller for TFT-LCD panel. The technology enables a single chip to support multiple display interfaces, reducing system cost and complexity. It also provides higher data transfer rates, low power consumption, and compatibility with a wide range of devices.

Features

- Supports for 120Mbps to Max 4Gbps data rate

- Supports Power Down Mode and Low-Power Mode during V-blank period

- Programmable differential transmitter output impedance (75ohm ~ 180ohm)

- Programmable different transmitter output amplitude (max 6dB)

- Jitter Injector included for debugging feature

- Built-in self-test (BIST) including pseudo random bit stram (PRBS) generation and checker

Tech Specs

| Foundry Node | 28nm | 14nm | 8nm |

|---|---|---|---|

| Standard | Clarity Post-NDA | ||

| Max. datarate | |||

| Status | |||