PCle

퀄리타스반도체는 PCIe (Peripheral Component Interconnect Express) 솔루션에 초점을 맞춘 초고속 인터커넥트 기술을 제공합니다. PCIe 규격은 다양한 주변 기기와의 연결을 위한 인터커넥트 기술로 매 버전이 증가할 때마다 데이터 전송 속도는 두배씩 증가하여 6.0 버전에서는 64Gbps에 이르는 초고속 전송을 지원합니다. 인공지능, 자동차, 데이터 센터, 스토리지, 모바일 등 다양한 분야에서 고대역폭과 저지연 통신에 대한 수요가 증가함에 따라 더욱이 활용이 늘어나고 있습니다.

퀄리타스반도체는 8nm FinFET공정에서 PCIe 4.0 PHY IP를 제공하고 있으며, 14nm, 5nm, 4nm 공정으로 확장할 계획입니다. 또한, 5nm 공정에서 DSP기반의 PCIe 6.0 PHY를 개발하고 있습니다.

PCle 6.0

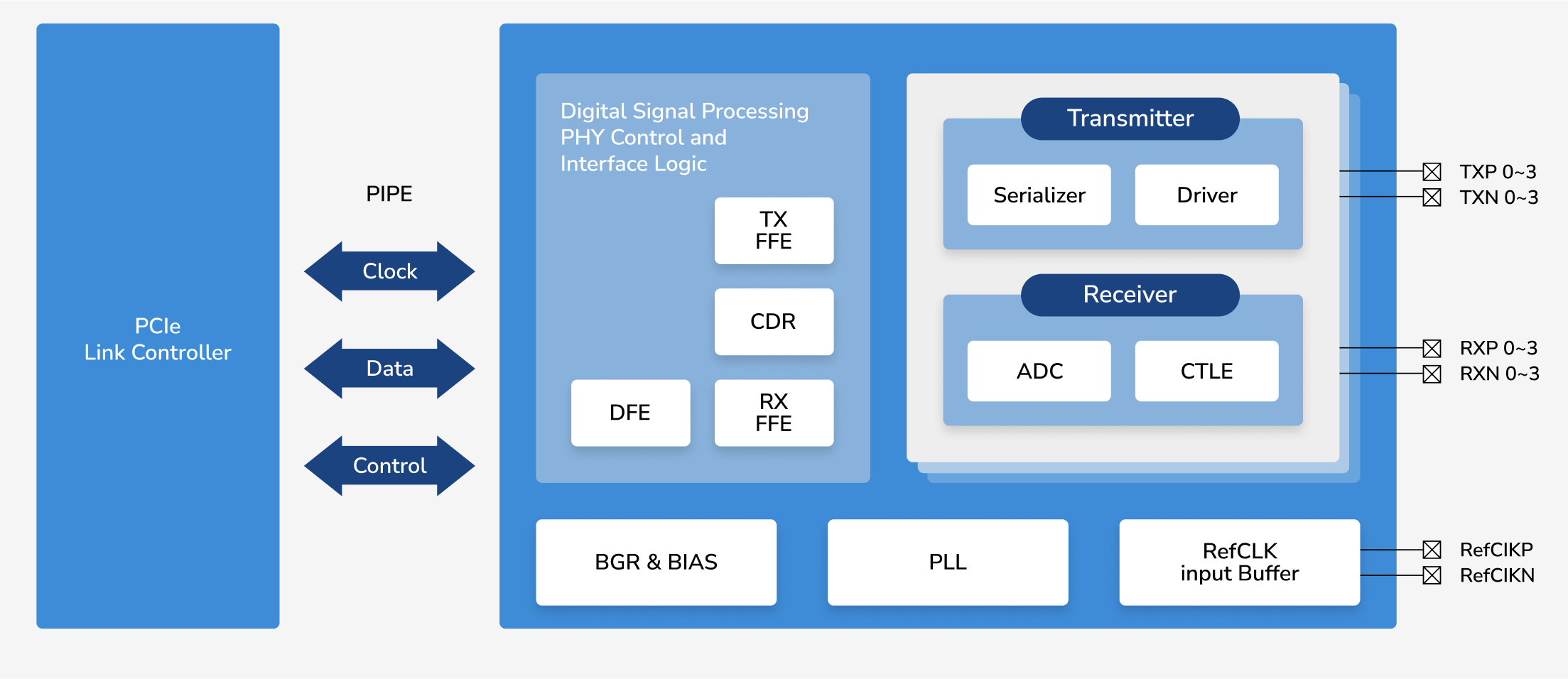

Request DatasheetQualitas' PCIe 6.0 PHY IP consists of hardmacro PMA and PCS compliant to PCIe Base 6.0 specification. This IP offers a cost-effective and low-power solution using FinFET CMOS technology. It includes all ESD I/Os and bump pads and supports extensive built-in self test features such as loopback and scan.

Features

- Compliant to PCIe Base 6.0 and PIPE 6.2

- Support Gen1, Gen2, Gen3, Gen4, Gen5 and Gen6

- Lane configuration

Common (CMN) and 1, 2 or 4 Data Lanes - Support high-resolution multi-tap FFE in transmitter

- Support CTLE, DSP-based multi-tap FFE and 1-tap DFE for channel equalization in receiver

- Support adaptive channel equalization

- 100MHz reference clock is required (support differential input buffer)

- Built-in self test feature capable of generating and checking PRBS patterns

- PCS included in PHY hardmacro

Tech Specs

| Foundry Node | 5nm |

|---|---|

| Standard | Disclosure After NDA |

| Max. datarate | |

| Status |

PCle 4.0

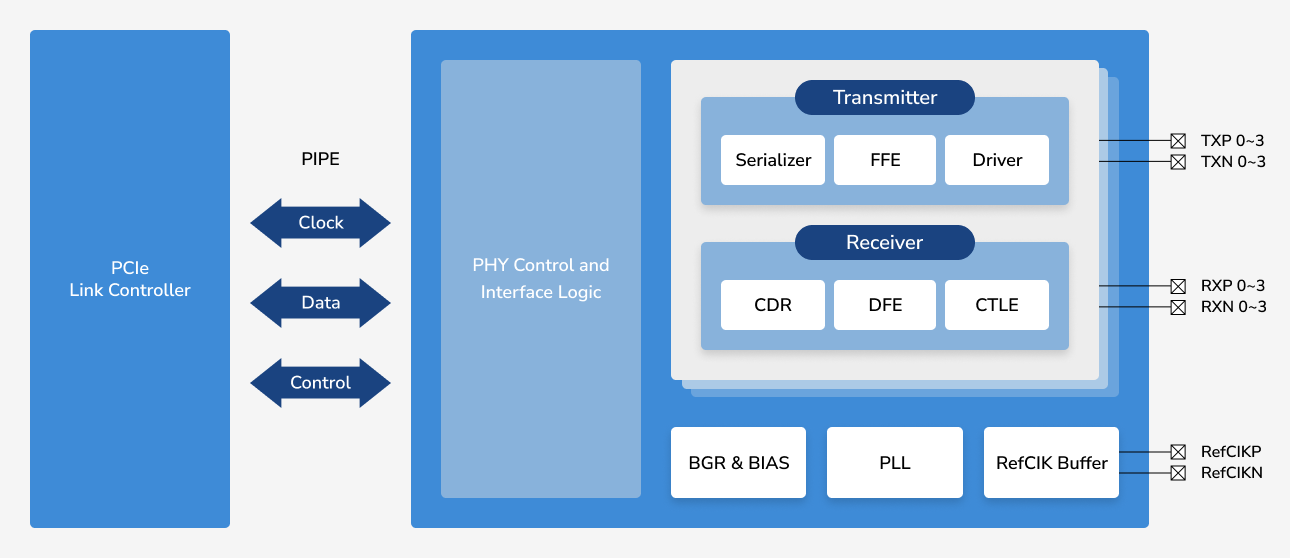

Request DatasheetQualitas' PCIe 4.0 PHY IP consists of hardmacro PMA and softmacro PCS compliant to PCIe Base 4.0 specification. This IP offers a cost-effective and low-power solution using FinFET CMOS technology. It includes all ESD I/Os and bump pads and supports extensive built-in self test features such as loopback and scan.

Features

- Compliant to PCIe Base 4.0 and PIPE 4.4.1 specification

- Support Gen1, Gen2, Gen3 and Gen4

- Lane configuration

Common (CMN) and 1, 2 or 4 Data Lanes - Support both aggregation and bifurcation modes (5nm PCIe 4.0 PHY only)

4-Lane PHY: 4-Lane aggregation or 2-Lane/2-Lane bifurcation

2-Lane PHY: 2-Lane aggregation or 1-Lane/1-Lane bifurcation - Support high-resolution multi-tap FFE in transmitter

- Support CTLE and 5-tap DFE for channel equalization in receiver

- Support adaptive channel equalization

- 100MHz reference clock is required (Support differential input buffer)

- Built-in self test feature capable of generating and checking PRBS patterns

- Compatible PCS is supported in softmacro form

Tech Specs

| Foundry Node | 8nm | 5nm |

|---|---|---|

| Standard | Disclosure After NDA | |

| Max. datarate | ||

| Status | ||