MIPI

Qualitas Semiconductor offers a variety of MIPI IP solutions, including the widely used CSI and DSI interfaces, for mobile, IoT, and automotive fields. The MIPI (Mobile Industry Processor Interface) standard targets high-speed interconnection between all semiconductor components embedded in mobile devices, such as modems, APs, cameras, displays, audio, storage, antennas, and tuners. Today, its application has expanded to various fields including AI and autonomous driving.

Qualitas Semiconductor offers MIPI IP for various FinFET semiconductor processes, including 28nm CMOS and D/C-PHY Combo PHY IP for 8nm, 5nm and 4nm processes.

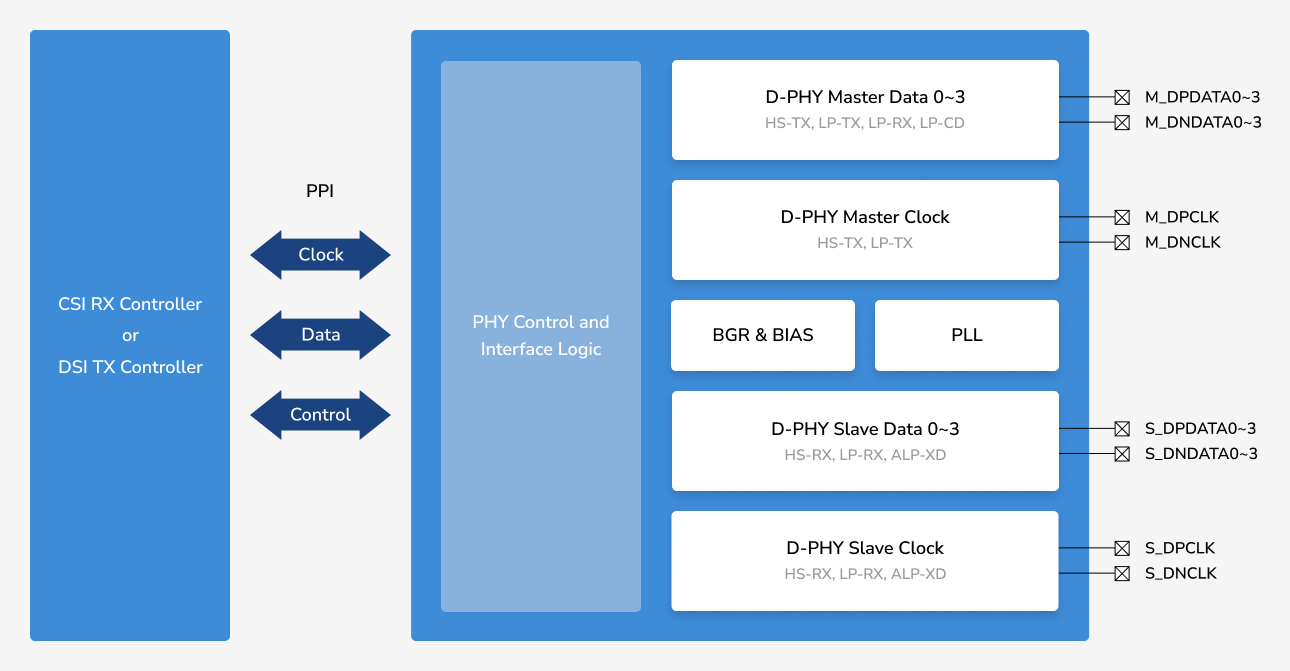

MIPI D-PHY

Request DatasheetQualitas' MIPI D-PHY IP is a hard-macro PHY for CSI RX and DSI TX. IO pads and EDS structures are included. Extensive built-in self-test features such as loopback and scan support. It offers a cost-effective and low-power solution.

Features

- Fully supports MIPI D-PHY HS-TX, HS-RX, LP-TX, LP-RX, and ULPS

- Supports lane configurations according to the user's demands

- Global operation timing parameters control

- Backward compatible with previous versions

- Built-in self-test feature producing and checking PRBS random pattern

- Low-power consumption and small area

- Highly validated structure in various processes

Tech Specs

| Foundry Node | 28nm | 14nm | 8nm | 5nm | 4nm |

|---|---|---|---|---|---|

| Standard | Under NDA | ||||

| Max. datarate | |||||

| Status | |||||

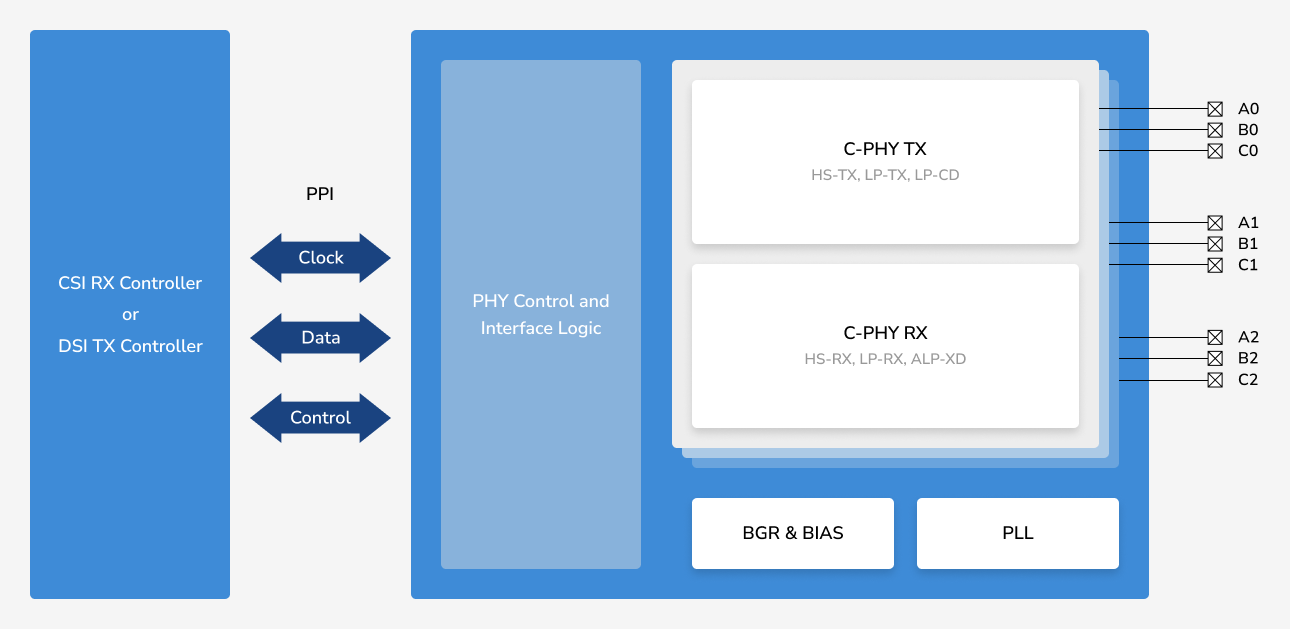

MIPI C-PHY

Request DatasheetThe MIPI C-PHY IP is a hard-macro PHY for CSI RX. IO pads and ESD structures are included. Extensive built-in self-test features such as loopback and scan support. It offers a cost-effective and low power solution.

Features

- Fully supports MIPI HS-TX, HS-RX, LP-TX, LP-RX, ULPS, and ALP

- Support lane configurations according to the user's demands

- Global operation timing parameters control

- Backward compatible with previous versions

- Built-in self-test features producing and checking PRBS random pattern

Tech Specs

| Foundry Node | 28nm | 14nm | 8nm | 5nm | 4nm |

|---|---|---|---|---|---|

| Standard | Under NDA | ||||

| Max. datarate | |||||

| Status | |||||

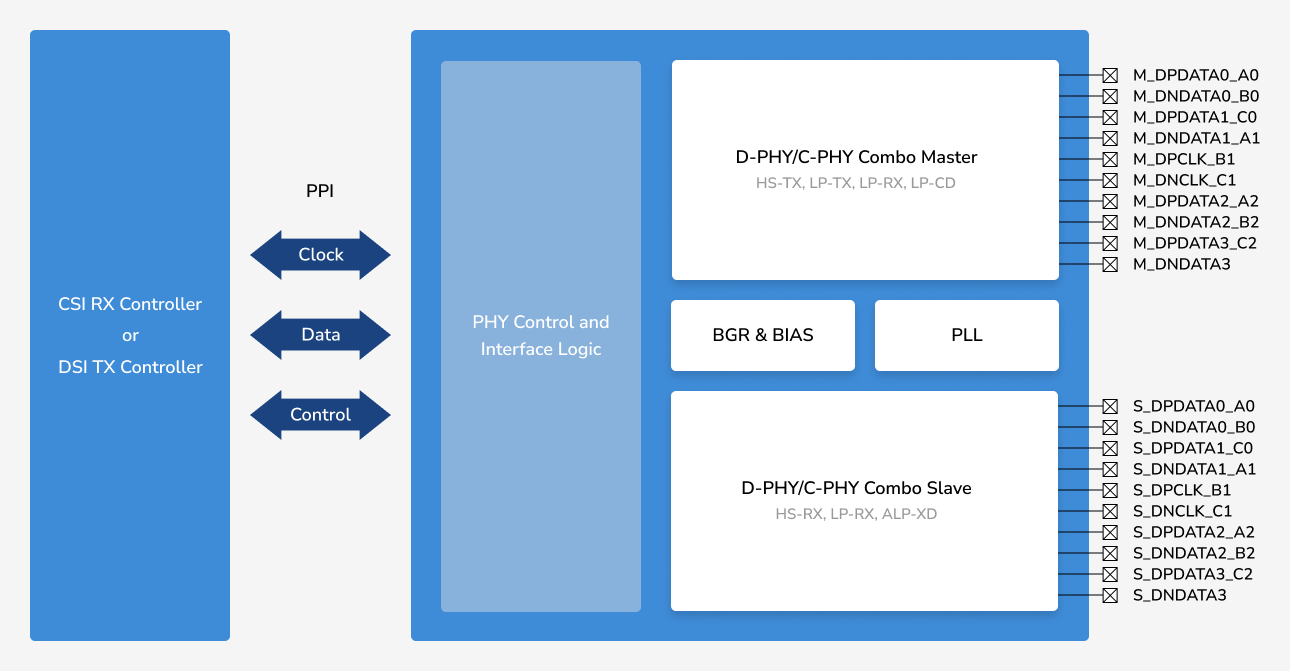

MIPI D-PHY/C-PHY Combo

Request DatasheetQualitas' MIPI D-PHY/C-PHY combo PHY IP is a hard-macro PHY for CSI RX or DSI TX. IO pads and ESD structures are included. Extensive built-in self-test features such as loopback and scan support. It offers a cost-effective and low-power solution.

Features

- Fully supports MIPI D-PHY HS-TX, HS-RX, LP-TX, LP-RX, and ULPS

- Supports lane configurations according to the user's demands

- Global operation timing parameters control

- Backward compatible with previous versions

- Built-in self-test feature producing and checking PRBS random pattern

- Low-power consumption and small area

- Highly validated structure in 8nm and under

Tech Specs

| Foundry Node | 14nm | 8nm | 5nm | 4nm | |

|---|---|---|---|---|---|

| Standard | Under NDA | ||||

| Max. datarate (D-PHY) |

|||||

| Max. datarate (C-PHY) |

|||||

| Status | |||||

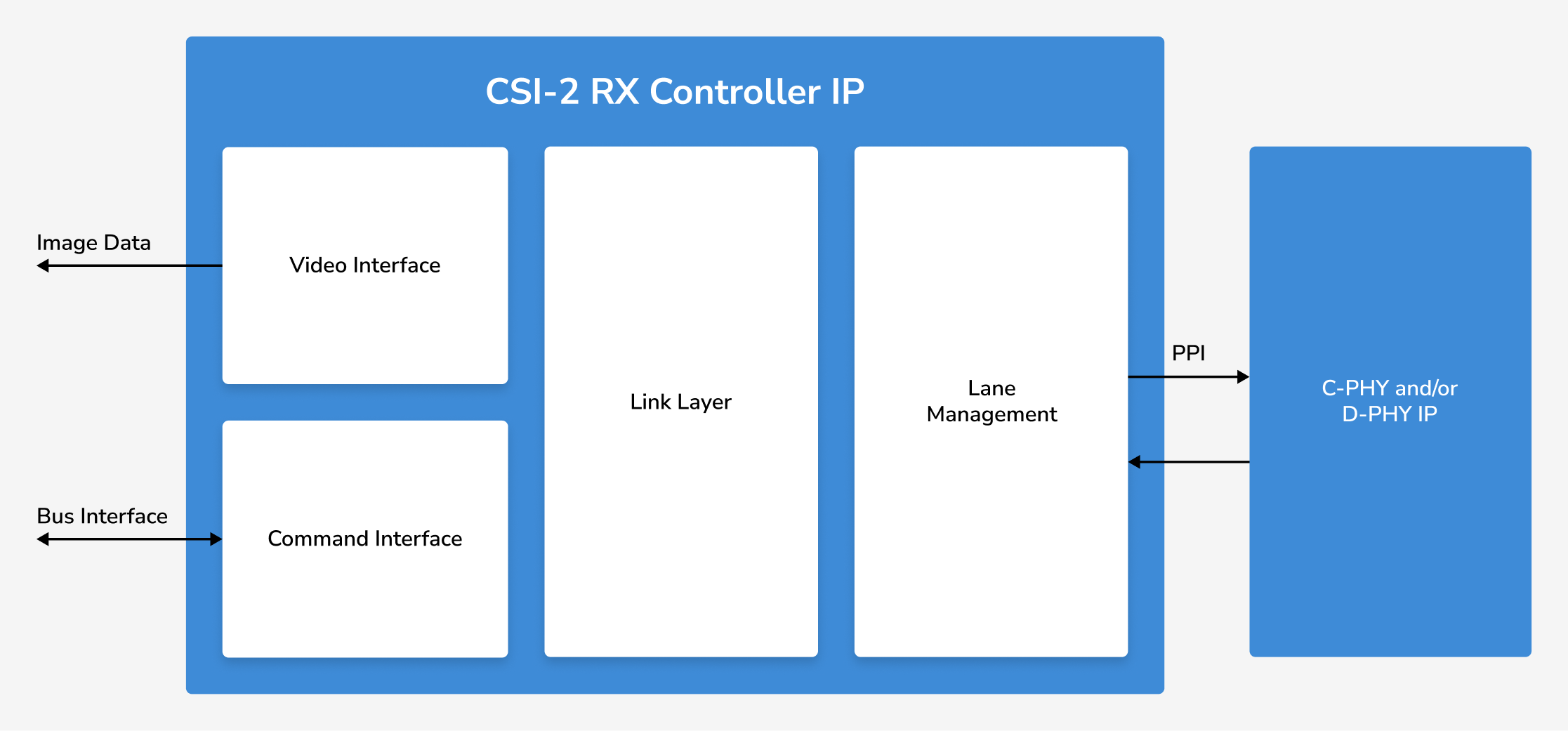

CSI-2 RX Controller

Request DatasheetThe Qualitas CSI-2 RX controller IP optimized for low power, small size and high-speed interface that supports a wide range of higher image resolutions. The CSI-2 RX Controller IP is fully compliant with CSI-2 v1.2 specification and supports DPHY v2.0 and the CPHY v1.2.

Features

- Compliant with the following MIPI specifications

MIPI CSI-2 specification v1.2 - PHY interface features

Supports MIPI DPHY v2.0, 1 to 4 DPHY data lanes

Supports MIPI CPHY v1.2, 1 to 3 CPHY data trios

Supports ULPS Mode - Link layer features

Supports of DPHY or CPHY by user configuration

Provides lane merging, error detection and correction, virtual channel detection, programmable data extraction and embedded data separation

Supports for all packet level errors and protocol decoding level errors

Supporting pixel formats : RGB888, Loosely Packed RGB666, RGB565, YUV422 (8bit)

DSI-2 TX/RX Controller

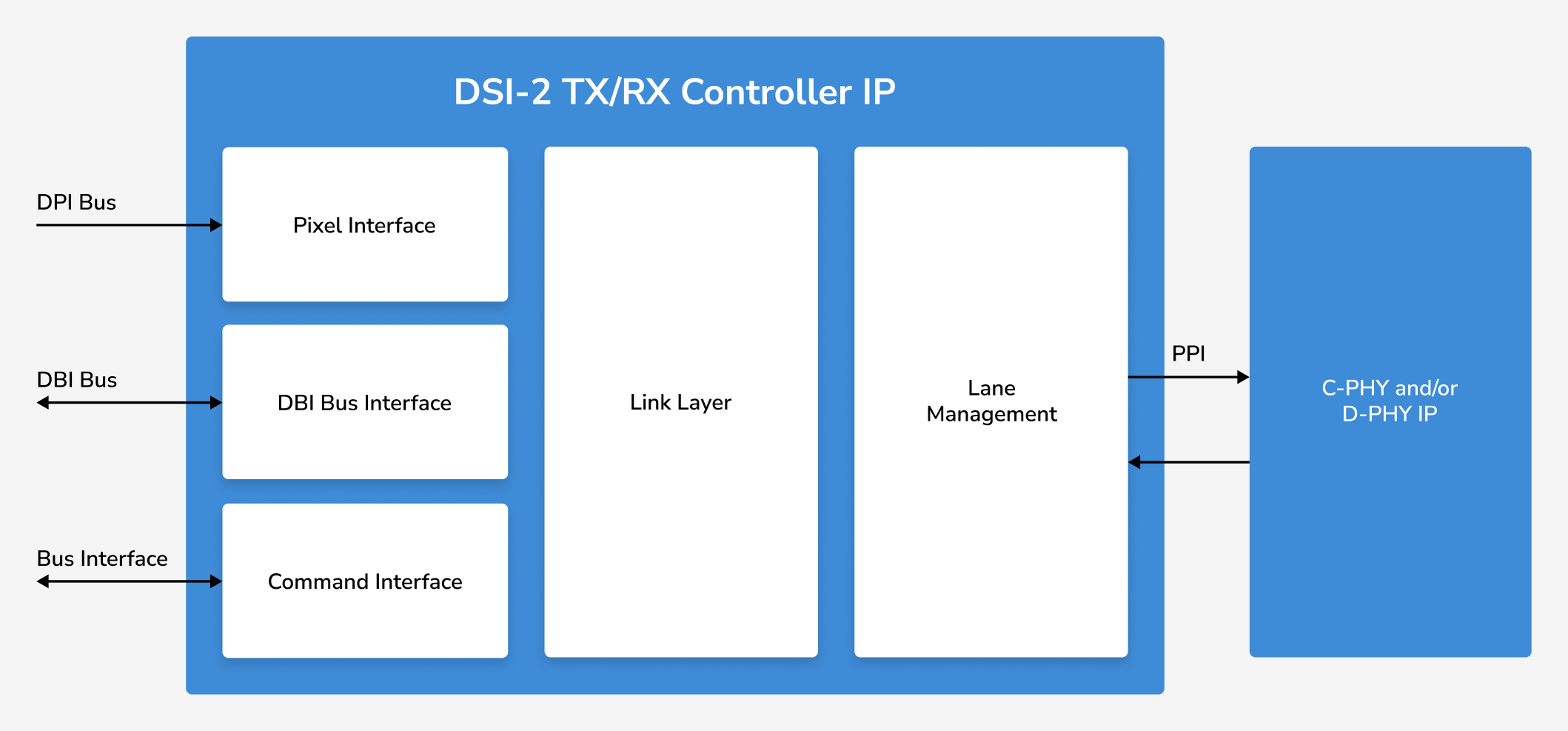

Request DatasheetThe Qualitas DSI-2 TX/RX controller IP optimized for low power, small size and high-speed interface between an application processor and display modules using either MIPI CPHY or MIPI DPHY. The DSI-2 TX/RX Controller IP is fully compliant with DSI-2 v1.1 specification and supports DPHY v2.0 and the CPHY v1.2.

Features

- Compliant with the following MIPI specifications

MIPI DSI-2 specification v1.1

Display Serial Interface (DSI-2) v1.0

Display Pixel Interface (DPI-2) v2.0

Display Bus Interface (DBI) v2.0

Display Command Set (DCS) v1.4 - PHY interface features

Supports MIPI DPHY v2.0, 1 to 4 DPHY data lanes

Supports MIPI CPHY v1.2, 1 to 3 CPHY data trios

Supports ULPS/LPDT/LPDR/BTA mode - Link layer features

Multiple peripheral support capability with configurable virtual channels

ECC and checksum capabilities

Supporting pixel formats : RGB565, RGB666 packed and loosely, RGB888