SERDES

To overcome the limitations of operating speeds and bandwidth, Qualitas Semiconductor is developing the latest SERDES PHY design technology. The 100G SERDES PHY IP provides essential functionalities required in various high-speed interconnect standards. Among data transmission encoding methods, the demand for PAM4 (Pulse Amplitude Modulation with 4 levels) is rising compared to NRZ (Non-Return to Zero), and Qualitas Semiconductor is also increasing the data transfer speed by implementing PAM4 through Ethernet and PCIe.

Qualitas Semiconductor develops analog CDR methods and DSP 100G SERDES PHY IP, providing optimized solutions depending on the client's needs. With the acquisition of next-generation technologies, Qualitas Semiconductor aims to expand its business further in the field of high-speed interconnects.

100G PAM4 SERDES PHY

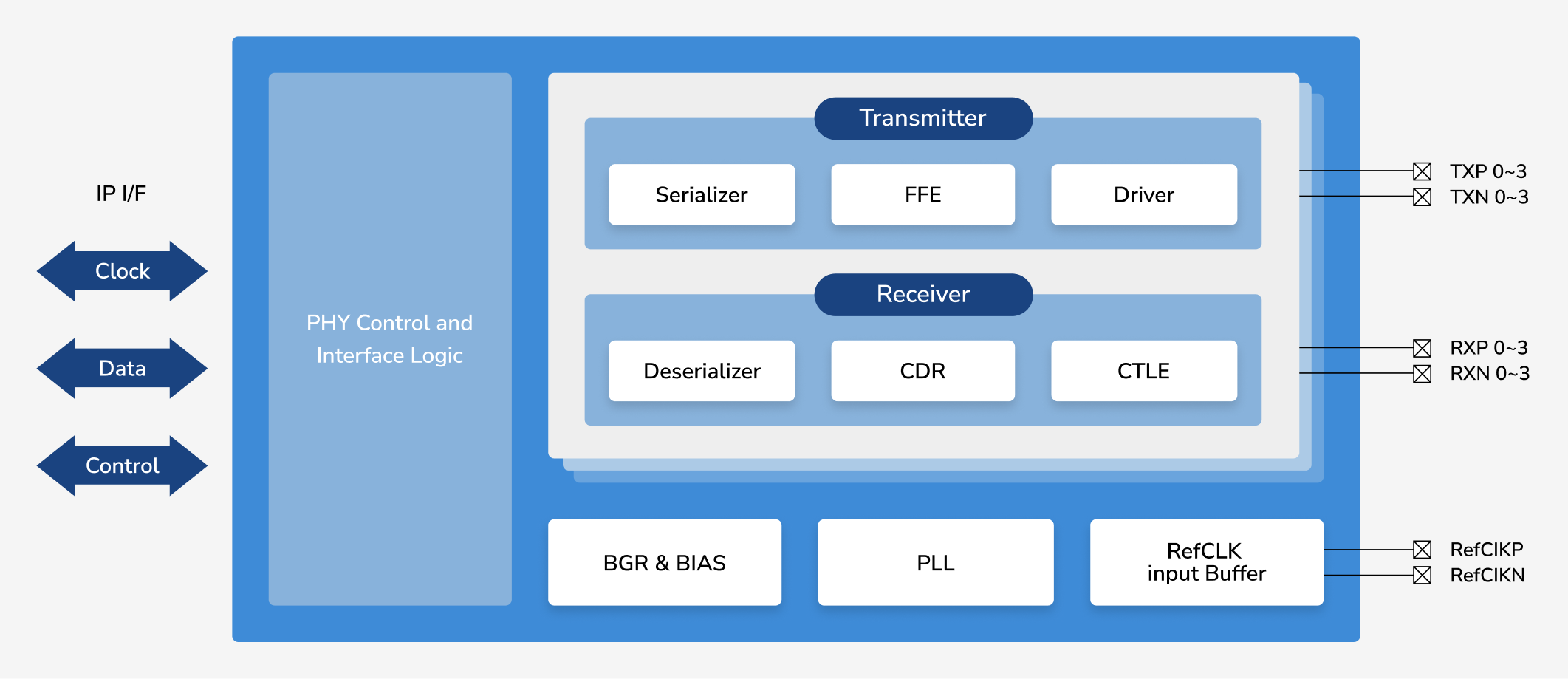

Request DatasheetQualitas' 100G SERDES PHY IP for VSR supports up to 100Gbps data rate with low power consumption and a small footprint. It has advanced features such as equalization, clock and data recovery and ensuring reliable data transmission. The IP can be integrated into a variety of applications such as networking, data centers, and high-performance computing.

Features

- Up to 12dB of insertion loss

- Common (CMN) and 1, 2 or 4 Data Lanes

- Supports 100 and 50G PAM4 and 50 and 25G NRZ

- RX CTLE/VGA and TX FIR Filters for Channel Equalization

Tech Specs

| Foundry Node | 14nm |

|---|---|

| Standard | Under NDA |

| Max. datarate | |

| Status |